CPLDとは?構造・FPGAとの違い・メリットなどを解説!

2025年8月3日更新

この記事を書いた人

大手メーカー「コマツ」、「オムロン」などで7年間、アナログ回路エンジニアとして設計・評価業務に従事。

ECU、PLCなどのエレキ開発経験を多数持つほか、機械商社での就労経験も有する。

株式会社アイズ運営の機電系フリーランスエンジニア求人情報「FREEAID」専属ライターとして、

機電分野の知識と実務経験を活かし、専門性の高い記事執筆を行っている。

半導体デバイスの1つであるCPLDをご存知でしょうか。今回は半導体設計に携わっていない人には聞き馴染みのないデバイスであるCPLDについて、類似用語との違いやメリットなどにも触れながら基本的な内容を解説します。

CPLDとは

CPLDとはコンプレックス・プログラマブル・ロジック・デバイスの略で、ユーザー自身が自由にプログラムできるデバイス、プログラマブル・ロジック・デバイス(PLD)の一種です。名前に含まれるコンプレックスが「複雑な」という意味からも分かるように、PLDの中では比較的複雑な回路設計が可能な素子のことを指します。ちなみにPLDにはさらに構造や回路規模が異なるFPGAという素子も存在します。

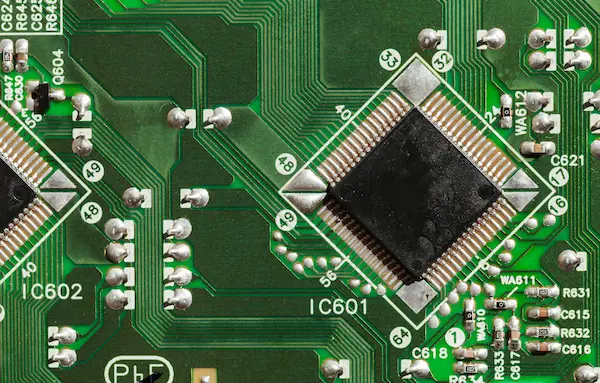

CPLDの基本的な構造と特徴

CPLDはマクロセルと呼ばれる論理機能を持ったブロックが、スイッチマトリクスと呼ばれる配線網によって相互に接続された構造をしています。マクロセルにはANDやOR、フリップフロップといった基本的な機能の論理素子が内蔵されており、ユーザーが指定したマクロセルを信号が順番に通過することで演算処理が行われます。

演算に掛かる時間は経由したマクロセルやスイッチマトリクスの数によって決まるため、無駄のない最適化された経路で回路を構築するのが重要です。CPLDではメモリ素子に不揮発性メモリの一種であるEEPROMセルを採用しており、素子自体の電源を落としても内部データが消えることはありません。

FPGAとの違い

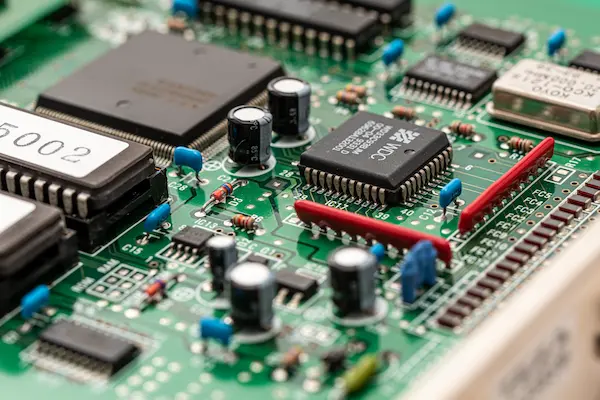

続いて、混同されがちなFPGAとの違いについても言及します。FPGAはロジックエレメントと呼ばれる論理ブロックが縦横に走る配線構造の間に配置された構造をしています。メモリ素子には揮発性メモリとして知られるSRAMを採用しており、通電している間はデータを保持するものの、電源供給が断たれるとデータが消失してしまいます。そのため、FPGAでは電源を投入するたびにプログラムを書き込むコンフィグレーション(設定)動作が必要です。

CPLDとFPGAの回路規模はゲート数と呼ばれる数値によって比較され、CPLDは数千から数万程度のゲート数であるのに対し、FPGAは数万から数百万程度のゲート数があると言われています。ちなみにゲート数とはANDやORなどの論理素子がウェハー上にどれだけあるかを語るために用いられる単位で、ドレイン・ソース・ゲート端子を持つMOSゲート構造の数を表します。

ASICとの違い

CPLDやFPGAを調べていると、類似の素子としてASICも出てきます。ASICは汎用ICとPLDの中間のようなIC素子で、PLDと同様に必要な機能だけを盛り込んで自由に開発できるものの、一度開発が完了すると後から回路を修正することはできません。設計・開発の自由度という点ではCPLDやFPGAの方に軍配が上がりますが、価格や熱効率、サイズ面ではASICの方が優れるため、開発段階ではCPLDを使用して設計を行い、回路設計が落ち着いたらCPLDをASICに置き換えて最適化する、という使い方が一般的です。

CPLDを使用する3つのメリット

続いてCPLDを使用するメリットについて、FPGAや汎用のICよりも優れている点を3つに絞って解説していきます。

回路設計の自由度が高く最適化しやすい

CPLDを使う1つ目のメリットとして、PLD全般に言えることですが、既製品のICを使用するのに比べて回路設計の自由度が高い点が挙げられます。これにより設計途中で仕様が変更となっても素子を無駄にせず柔軟な設計が可能です。また仕様に合わせて最適な回路構成にすることで余計な論理ブロックや配線を最小限に抑えられ、最終的な製品サイズも小さくしやすいです。

電源投入してからの挙動が早く消費電力も抑えられる

2つ目のメリットとして、不揮発性メモリを使用しているためFPGAのようにコンフィグレーション動作を必要とせず、電源投入してすぐ使える点も挙げられます。これにより電源投入のあと最初にOSや基礎ソフトウェアをメモリに反映するブートストラップ的な使い方も可能で、FPGAのコンフィグレーションを行うための初期メモリとして使用することもあります。さらに電源を落としてもメモリデータが消えないため、使用しない時は給電を停止して消費電力を抑えることも可能です。

同一機能を実現する際に価格・納期・動作速度で優れる

CPLDとFPGAで同一の機能を実現する場合、CPLDの方が価格や納期、動作速度の面で優れることが多いです。既に触れたようにFPGAではコンフィグレーション動作の検討なども必要なため、CPLDの方が相対的に開発期間が短いケースがほとんどです。またCPLDの方が回路規模が小さいため価格も安価で、同じ論理演算にかかる処理速度も早い傾向にあります。製作納期や価格を抑えられれば素早い市場投入も期待できるため、ニッチな製品を生み出す上では非常に大きなメリットと言えるでしょう。

FPGAと比べた時のデメリットもある

CPLDはより高機能なFPGAに比べていくつかのデメリットも存在します。まず実装されている論理機能の数が少なく、組み込みシステムに搭載されるエンベデッドメモリや乗算器といった機能が搭載されていないことが多いです。また論理ゲートの数も劣っているため、より複雑な機能を実現したい場合にはFPGAに軍配が上がるでしょう。さらにFPGAでは回路集積度の高さを利用した並列処理も可能なため、時間を掛けて設計を行った場合であれば、例え同一機能を実現してもCPLDの方が動作速度が劣ることがあります。

CPLDを用いた回路設計の流れ

CPLDを用いた製作は大まかに、仕様の検討、デバイスやツールの選定、プログラム、デバックといった流れで行われます。最初の仕様検討ではデバイスにCPLDを使用するのが適切かどうかも考慮しながら、回路の目的や入出力点数、演算能力などの仕様を明確にします。重要な点として、CPLDを使うことを前提に設計するのではなく、仕様的にFPGAを使う必要はないか、汎用ICで置き換えられないか、といった点も考慮して設計すると良いでしょう。

仕様が固まったら予算や使い勝手なども考慮しながら、具体的なCPLDのメーカーや方式、使用する開発ツールなどを決めていきます。これらの準備が整ったら実際にプログラムを行い、デバッグにてプログラムミスや部品同士の相性による不具合を潰しながら完成させていきます。ここでも単に目的通り動作することだけでなく、無駄な配線や挙動がないか探すなど、回路構成や動作を最適化するよう心がけましょう。

まとめ

今回はユーザーがプログラムを修正可能なロジックデバイス、CPLDについて解説してきました。FPGAとの違いやそれぞれの使い分けなど基本的な内容を理解し、コストや納期を抑えつつシンプルな回路を設計するにはCPLDが、納期やコストを掛けてでも複雑で高機能な回路を設計するにはFPGAが適していると理解できたと思います。製品によっても具体的な仕様は異なるので、より詳細を知りたい方は各種メーカーの情報を確認してみると良いでしょう。

当サイトFREE AIDは、機電系を始めとしたエンジニアのフリーランス専門求人を扱っています。

→機電系フリーランスエンジニア求人はこちら

また、フリーランスエンジニアとして働きたい方に合った案件探しや専門アドバイザーの活動サポートも無料で行っています。

→フリーランス無料支援に興味がある方はこちら

この記事の運営元:株式会社アイズ

「アウトソーシング」「ビジネスソリューション」「エンジニアリング」「ファクトリーオートメーション」の4つの事業を柱に、製造業やICT分野の課題解決を力強くサポートします。

フリーランスの機電系エンジニア求人情報サイト「FREE AID」を運営しています。

機電系求人はこちら

機電系求人はこちら

設計技術者(樹脂、金属部品)

- 単価

40~50万円

- 職種

- 機械設計

- 詳細を見る

FPGAの設計開発:電気電子設計

- 単価

70~80万円

- 職種

- 電気電子設計

- スキル

- ・FPGA論理設計、RTLコーディング、論理検証環境構築、論理検証・RTLコード:VHDL・論理検証ツール:Siemens製Questa/ModelSIM

- 地域

- 東京

- ポイント

- #高単価

- 詳細を見る

UI画面の設計業務:電気電子設計

- 単価

64〜万円

- 職種

- 開発

- 電気電子設計

- スキル

- 必要スキル: ・電源回路は複数回経験し、設計動作確認など、一人でもある程度やるべきことが分かる。 ・数十頁のデータシートを読み、要求仕様(タイミング/電圧など)が理解できる ・その他左記の回路の種類の中で、回路設計の実務経験が1回以上ある。 ・回路修正ができる(半田付け、ジャンパー処理)

- 地域

- 関西

- ポイント

- #業務委託#駅近

- 詳細を見る

【急募】工作機械メーカーにおける自社製品の制御設計

- 単価

40~50万円

- 職種

- 電気電子設計

- スキル

- 基本的なPCスキル産業用機械・装置の電気設計経験

- 地域

- 山梨県

- ポイント

- #業務委託

- 詳細を見る