半導体業界におけるCMP技術とは?仕組みや技術的な工夫について解説!

2025年5月10日更新

この記事を書いた人

大手メーカー「コマツ」、「オムロン」などで7年間、アナログ回路エンジニアとして設計・評価業務に従事。

ECU、PLCなどのエレキ開発経験を多数持つほか、機械商社での就労経験も有する。

株式会社アイズ運営の機電系フリーランスエンジニア求人情報「FREEAID」専属ライターとして、

機電分野の知識と実務経験を活かし、専門性の高い記事執筆を行っている。

半導体をナノメートル単位で平坦化し、微細加工の実現に大きく貢献するCMP(化学機械研磨)技術。どのような技術なのか、詳しく知りたい方もいるのではないでしょうか。そこで本記事では、CMP技術の概要から仕組み、どのような技術が用いられているかまでを初級者にもわかりやすく解説します。

CMPとは

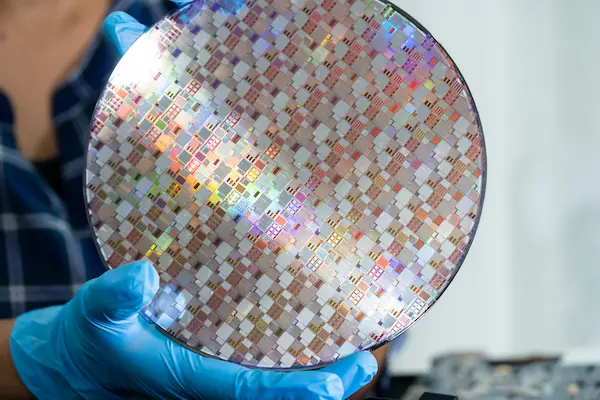

まず、CMPとは「Chemical Mechanical Polishing」の略で、化学的・機械的に半導体を研磨する手法のことを指します。CMP工程では、ヘッドにウェーハの裏面を吸着させて保持し、上から研磨パッドに押し付けながら移動・回転させることで研磨を行います。この時、研磨パッド側に研磨粒子を含むスラリーを流すことで研磨粒子とウェーハが接触し、研磨が進んでいきます。

また、CMPではスラリーに化学薬品を混ぜて化学的作用を発生させ、機械的研磨と複合させることでさらなる精密な平滑化を実現しています。化学的作用の役割は多岐にわたり、素材の表面を軟化させ加工スピードを上げる、凹部の研磨を防ぐなどといった効果が得られます。なお、半導体の研磨自体はCMP以外にも様々な手法がありますが、その中でも最も精密に平坦な研磨が行えることから、現在は基本的にCMPが用いられています。

CMPが求められる背景

続いて、なぜ半導体製造においてCMP技術が必要とされるのかを解説します。半導体はナノメートル単位の素子や配線を何層も積層することで作られています。積層構造は成膜とエッチングを繰り返すことで作られるため、そのたびに凹凸が生じてしまうと、次の層が変形してしまって正しく素子を形成できず、不具合の要因となってしまいます。そのため、ウェーハや成形した半導体層にCMPを行うことで、ナノレベルでの平坦化を実現し、全ての層が設計通りに正しく成膜されるようにしています。

CMP技術における工夫

CMPではスループットや平滑度を高めるため、素材や形状などに様々な工夫が行われています。ここからは、技術的に重要なポイントをいくつか紹介します。

研磨粒子

研磨粒子はウェーハと直接接触し、研磨の品質を左右する存在なので、不要な凸部を素早く削りつつ、余計な傷や凹凸を作らないことが求められます。まず材料には、研磨性能の良いシリカ(SiO2)やアルミナ(Al3O2)、セリア(CeO2)といった材料が使われます。

シリカは安価でかつオングストローム単位の小さな粒子が作れるなどの利点があり、ウェーハや銅などの研磨で多用されます。また、セリアはSiO2膜を迅速かつ平坦に研磨できる、アルミナは硬度が高く金属の加工に向いているといった特徴を持ち、研磨対象の材質に合わせた使い分けがされています。

また、砥粒のサイズは数nm~1μmほどの種類があり、求められる平滑度に応じた使い分けがされています。粒径が細かい方が高い平滑度が得られるほか、微細な傷も生じにくくなるメリットがありますが、その分加工に時間がかかるため、バランスを考えた粒径を選ぶ必要があります。また近年では半導体の微細化が進み、オングストローム単位の砥粒も使われるようになっています。

研磨パッド

研磨パッド自体は直接ウェーハに接触しませんが、研磨パッドの表面凹凸などでスラリーの動きも変化するため、研磨に大きな影響を与えます。そのため、材質や表面構造などに様々な工夫が行われています。

まず、研磨パッドの種類は硬さによって3種類に大別されます。最も硬いのは発泡・硬化させたポリウレタンを使ったポリウレタンパッドで、特に微細構造の平坦化に使われます。2番目は、不織布にポリウレタン樹脂を含ませて作る不織布パッドで、様々な硬さに調整することで幅広い用途で使われています。最も柔らかいのは、スポンジのように発泡させたポリウレタンパッドで、欠陥を除去する仕上げ加工などで使われています。

また、研磨パッドの表面処理も企業ごとで様々な工夫がされています。例えば、スラリーをパッド表面に適切に保持するため、表面に溝や穴を作ったり、ダイヤモンドなどの粒子を埋め込んだりすることで凹凸を作る場合があります。他にも、パッドの寿命を向上させたり、パッドからの金属イオンの流出を防いだりするためのコーティングを行うこともあります。

薬品による化学的作用

スラリーに投入される薬剤はCMPにおいて研磨をより効率化する役割を持っていますが、その効果は多岐にわたります。例えば、均一な研磨を実現する上では、砥粒をスラリー中で均一に分布させる分散剤が活躍しています。

他にも、半導体表面を脆くして研磨を進めやすくする酸化剤、凹部を研磨から守り、平坦化に寄与する界面活性剤などがあり、様々な方法で研磨をスムーズに進めやすくしています。また、研磨で生じた破片をスラリーに溶かしやすくし、除去を容易にする錯形成剤、研磨後の腐食を防止する防食剤など、研磨後に品質を保つような効果のある薬剤も利用されています。

CMP工程では研磨後のパーティクルの除去も重要

このように、ウェーハの平坦化のために行われるCMPですが、CMP工程全体でみると、研磨後に洗浄を行い、パーティクルを除去することも重要です。元々CMP技術はスラリーを使って作業を行いますが、これは工程において大量のパーティクル(ゴミ)が出ているのと変わりません。少しのパーティクルも許さない半導体製造工程とは相容れない概念なので、CMP装置は装置内部でのみスラリーを使い、研磨後はパーティクルが無い状態にしてから取り出すという作業を入れる必要があります。

現在はCMP装置内に洗浄・乾燥工程を入れ込むことで、処理前後どちらもウェーハを乾燥状態にする「ドライイン・ドライアウト」方式が一般的となっています。これにより、スラリーの影響を無視して利用できるようになっていますが、内部ではスラリーを外に出さないような工夫が行われていることは理解しておきましょう。

まとめ

今回は、半導体業界において重要なプロセスの一つである、CMP技術について解説しました。CMP技術とは化学機械研磨のことで、半導体をナノレベルで平坦にすることにより、微細な積層構造を正確に作れるようにする技術のことです。CMPは研磨粒子や薬剤の入ったスラリーを研磨パッドで押さえつけ、半導体を研磨するシンプルな手法ですが、素早く確実に研磨を行うために様々な工夫が凝らされています。メーカーのサイトなどを見れば各社の取組みが紹介されているので、詳しく知りたい方はぜひ調べてみて下さい。

当サイトFREE AIDは、機電系を始めとしたエンジニアのフリーランス専門求人を扱っています。

→機電系フリーランスエンジニア求人はこちら

また、フリーランスエンジニアとして働きたい方に合った案件探しや専門アドバイザーの活動サポートも無料で行っています。

→フリーランス無料支援に興味がある方はこちら

フリーランス×機電系エンジニア!高単価求人はこちら ▶

この記事の運営元:株式会社アイズ

「アウトソーシング」「ビジネスソリューション」「エンジニアリング」「ファクトリーオートメーション」の4つの事業を柱に、製造業やICT分野の課題解決を力強くサポートします。

フリーランスの機電系エンジニア求人情報サイト「FREE AID」を運営しています。

機電系求人はこちら

機電系求人はこちら

設計技術者(樹脂、金属部品)

- 単価

40~50万円

- 職種

- 機械設計

- 詳細を見る

FPGAの設計開発:電気電子設計

- 単価

70~80万円

- 職種

- 電気電子設計

- スキル

- ・FPGA論理設計、RTLコーディング、論理検証環境構築、論理検証・RTLコード:VHDL・論理検証ツール:Siemens製Questa/ModelSIM

- 地域

- 東京

- ポイント

- #高単価

- 詳細を見る

UI画面の設計業務:電気電子設計

- 単価

64〜万円

- 職種

- 開発

- 電気電子設計

- スキル

- 必要スキル: ・電源回路は複数回経験し、設計動作確認など、一人でもある程度やるべきことが分かる。 ・数十頁のデータシートを読み、要求仕様(タイミング/電圧など)が理解できる ・その他左記の回路の種類の中で、回路設計の実務経験が1回以上ある。 ・回路修正ができる(半田付け、ジャンパー処理)

- 地域

- 関西

- ポイント

- #業務委託#駅近

- 詳細を見る

【急募】工作機械メーカーにおける自社製品の制御設計

- 単価

40~50万円

- 職種

- 電気電子設計

- スキル

- 基本的なPCスキル産業用機械・装置の電気設計経験

- 地域

- 山梨県

- ポイント

- #業務委託

- 詳細を見る