JTAGと呼ばれる規格とは?検査方法や技術的要素も解説!

2024年8月20日更新

この記事を書いた人

大手メーカー「コマツ」、「オムロン」などで7年間、アナログ回路エンジニアとして設計・評価業務に従事。

ECU、PLCなどのエレキ開発経験を多数持つほか、機械商社での就労経験も有する。

株式会社アイズ運営の機電系フリーランスエンジニア求人情報「FREEAID」専属ライターとして、

機電分野の知識と実務経験を活かし、専門性の高い記事執筆を行っている。

JTAGと呼ばれる規格を耳にしたことはあるでしょうか?半導体パッケージのテストに関する規格で、規格を生み出した団体名を基に名称が付けられました。今回はJTAG規格について、誕生した背景や具体的な規格の内容に触れながら解説していきます。

JTAGとは何か?誕生の背景も解説!

まずはJTAGという単語について、誕生した背景や意味にも触れながら解説します。なお、JTAGは製品名など様々な意味で使われることもありますが、今回は元々の意味である半導体パッケージの検査規格(および規格を生み出した団体名)に特化して説明します。

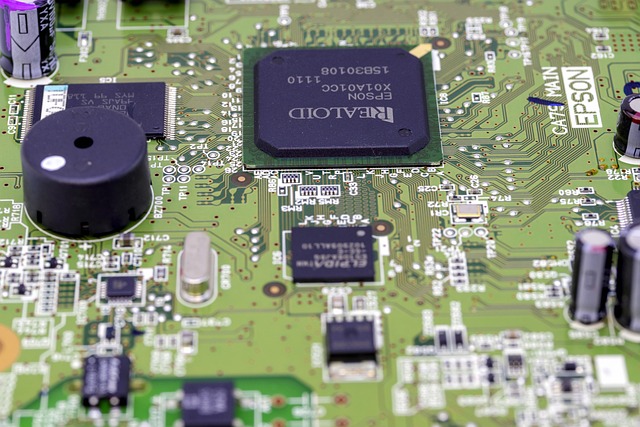

半導体パッケージの集積化に伴うテスト問題

JTAGは半導体パッケージの集積化が加速し、基板検査が高難易度化したことで誕生しました。半導体パッケージとは、半導体チップを保護しつつプリント基板上にはんだ付けできるように構成された素子で、ピンと呼ばれるはんだ付け用の足があるのが特徴的です。20世紀後半に生み出されたSOPやDIP、QFPなどの種類では基本的にピンがパッケージ外側に出ているため、はんだ付け不良は外観検査などで容易に見つけることができました。

しかしピンをパッケージの裏側に配置したBGAが誕生すると、基板へ実装した状態ではんだ不良などを検出するのが難しくなり、JTAGという団体が専用のテスト規格を生み出すきっかけとなりました。

JTAGは検査手法に関する規格と団体の名称

半導体検査の課題を打破する目的で発足したJTAGは、ヨーロッパ企業が先頭に立って発足したため初めのうちはJETAG(Joint European Test Action Group)という名称でした。しかし発足してすぐにアメリカ企業も加わったため、名前からEuropeanが外れて現在のJTAGという名称に落ち着きます。

同団体は当初の目的である実装状態でのピン検査を行うための手法として「バウンダリスキャン」と呼ばれる方法を編み出し、IEEE1149.1という規格の確立にまで至りました。このような背景から元は団体名だったJTAGという名称が、生み出された検査方法や規格も含めて指す言葉として浸透しています。

JTAGテストの内容

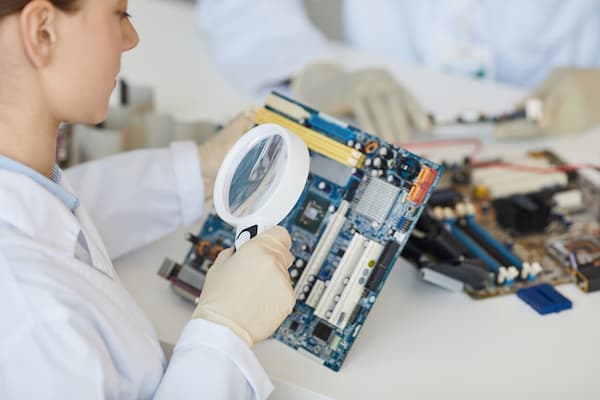

JTAGテストとして知られるバウンダリスキャンテストは、テストアクセスポートと呼ばれる専用のI/Oポートから信号を入出力して実行されます。基本的なテストは演算装置であるロジックコアと入出力ポート間に設置されたバウンダリ・スキャンセルを動作させ、はんだ不良や部品内部の断線、回路の誤り、配線同士の短絡などの不良を検知します。

JTAGテストにはJTAGテストに対応した半導体パッケージと、部品表や回路情報から作られたテストパターンが必要ですが、最近ではテストパターンを自動的に生成してくれるテストツールも登場したため、以前に比べてJTAGテストの敷居は低くなりました。

JTAGテストがもたらした意外なメリット

BGAなどの半導体パッケージをテストするために生み出されたJTAGテストですが、本来の目的とは異なるメリットももたらしました。例えば、JTAGテスト対応デバイスを使えば、JTAGに非対応のデバイスも検査することができます。

基本的にJTAGテストは対応する半導体パッケージにしか使えないため、非対応デバイスをダイレクトに制御することはできません。しかし、テストツールによってJTAG対応デバイスをテスト機器として模擬的に動かすことで、基板上で接続している他の非対応デバイスもテストできるようになりました。もちろん確認できる内容や範囲は限られますが、既に実装された基板上で簡易的なテストを行いたい時には役に立つ機能と言えるでしょう。

他にもインシステムプログラミングと呼ばれる、JTAGデバイスを基板上に実装したまま内部プログラムを書き換える機能も実装できるようになりました。これまで基板へ実装された状態でデバイス内のプログラムを書き換えるには、専用のプログラマや入出力用ソケットが必要でしたが、JTAGデバイスに拡張機能を実装すれば特殊な機器なしにメモリ内部を書き換えられるため、デバイスのアップデートやソフトの書き換えが容易になりました。

JTAGテストに必要な要素

JTAG規格に対応したデバイスでは、JTAGテストを可能にするために必要な要素がいくつかあります。具体的な用途にも触れながらそれぞれ解説していきます。

テストアクセスポートとコントローラ

JTAGテストに対応したデバイスには、テストアクセスポートと呼ばれる専用の入出力ポートが存在します。具体的にはJTAGテストの動作クロックを制御するTCK(テストクロック)、テスト用の信号を入力するTDI(テストデータイン)、JTAGデバイス内部からの信号を出力するTDO(テストデータアウト)、JTAGテストデバイスの状態を決めるTMS(テストモードセレクト)などです。

また、JTAGデバイスへ電源を供給するVccピンや、オプションでテストアクセスポートコントローラの状態を強制的にリセットできるTRST(テストリセット)などのポートも存在します。また、JTAGデバイスの動きを決める回路はテストアクセスポート(TAP)コントローラと呼び、TCK信号が立ち上がるタイミングのTMS信号に応じてデバイスの動作をコントロールします。

データレジスタ

JTAGデバイスにはテストに必要なデータを保持するレジスタも存在します。まずTDIポートから入力された命令データを格納するのがインストラクションレジスタで、信号の処理方法やデータの受け渡し先の指定など、TAPコントローラに対する命令を保持します。また基本的なデータを保持するためのデータレジスタも3つ用意されており、1つ目のデータレジスタはJTAGデバイスの各I/Oピンとコアロジックとの間のデータ読み書きを目的としたバウンダリスキャンレジスタです。

2つ目のデータレジスタはJTAGデバイスから他のデバイスに信号を送るときに使用するバイパスレジスタで、TDIポートから入力された命令データをダイレクトにTDOポートへ送信します。最後のデータレジスタはIDCODEレジスタで、デバイスの型式や製造番号などの基礎的なデータが保管されています。また、JTAGデバイスによってはこれら以外のレジスタがオプションとして搭載されているケースも多いです。

まとめ

今回は基板上へ既に実装された半導体パッケージのはんだ不良や基板不良などのテストを目的としたJTAG規格について、発足した経緯や団体にも触れながら解説しました。JTAGはテスト規格としてだけでなくJTAG非対応デバイスの簡易的な試験やJTAGデバイスの内部プログラム書き換えにも使える便利な規格です。今後も半導体基板の集積度はますます向上し、JTAGテストが更に重要な存在になると予想されるので、しっかりと内容を理解しておきましょう。

フリーランス×機電系エンジニア!高単価求人はこちら ▶

この記事の運営元:株式会社アイズ

「アウトソーシング」「ビジネスソリューション」「エンジニアリング」「ファクトリーオートメーション」の4つの事業を柱に、製造業やICT分野の課題解決を力強くサポートします。

フリーランスの機電系エンジニア求人情報サイト「FREE AID」を運営しています。

機電系求人はこちら

機電系求人はこちら

設計技術者(樹脂、金属部品)

- 単価

40~50万円

- 職種

- 機械設計

- 詳細を見る

FPGAの設計開発:電気電子設計

- 単価

70~80万円

- 職種

- 電気電子設計

- スキル

- ・FPGA論理設計、RTLコーディング、論理検証環境構築、論理検証・RTLコード:VHDL・論理検証ツール:Siemens製Questa/ModelSIM

- 地域

- 東京

- ポイント

- #高単価

- 詳細を見る

UI画面の設計業務:電気電子設計

- 単価

64〜万円

- 職種

- 開発

- 電気電子設計

- スキル

- 必要スキル: ・電源回路は複数回経験し、設計動作確認など、一人でもある程度やるべきことが分かる。 ・数十頁のデータシートを読み、要求仕様(タイミング/電圧など)が理解できる ・その他左記の回路の種類の中で、回路設計の実務経験が1回以上ある。 ・回路修正ができる(半田付け、ジャンパー処理)

- 地域

- 関西

- ポイント

- #業務委託#駅近

- 詳細を見る

【急募】工作機械メーカーにおける自社製品の制御設計

- 単価

40~50万円

- 職種

- 電気電子設計

- スキル

- 基本的なPCスキル産業用機械・装置の電気設計経験

- 地域

- 山梨県

- ポイント

- #業務委託

- 詳細を見る